|

|

|

1.バウンダリスキャン概要

1.1 はじめに

バウンダリスキャンテストは、1985年にヨーロッパのJETAG(Joint European Test Action Group)によって最初に提案されました。さらに1986年に米国企業のメンバが加わり、1990年に規格化されたのがIEEE std 1149.1−1990 Standard Test Access Port and Boundary−Scan Architectureです。この規格は、正式名称よりも、その作業グループの名称であるJTAG(Joint Test Action Group)が、規格名称であるかのように使われていますが、JTAGはあくまで作業グループの名称です。

バウンダリスキャンテストが制定された当初は、対応するデバイスが少なく、又PCBの製造性がよい日本国内ではあまり普及しませんでした。しかし、昨今ではデバイスパッケージの高密度化(多ピン化、BGA化)がすすみ、バウンダリスキャンに対応するデバイスが増えてきました。又CPUのインサーキットエミュレータ、FPGAのプログラムインターフェースにもバウンダリスキャンが使用されるようになってきています。

IEEE std 1149.1 Standard Test Access Port and Boundary−Scan Architectureは1993年、1995年、2001年に改訂されており、最新の規格はIEEEホームページ http://www.ieee.org を参照して下さい。

1.2 バウンダリスキャン試験の原理

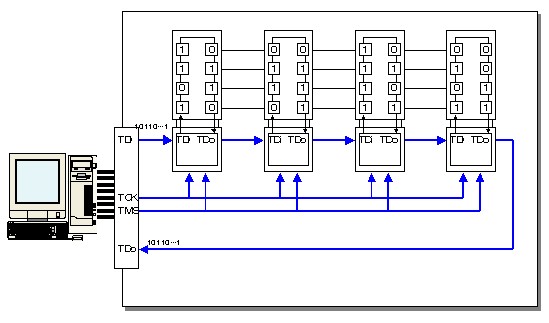

バウンダリスキャンテストはPCB上のバウンダリスキャン対応デバイスを一筆書き(デイジーチェイン)に接続し、外部からデバイスの入出力をコントロールすることで、PCB上のデバイスの試験を行なうものです。試験を行なうにはPCBに接続されたボードテスタ(PCやWS)からの4本の信号で試験の実行が行なわれます。

ボードテスタからのTDi信号はPCB上のバウンダリスキャンデバイスのTDiピンに接続されTDoピンから出力されます。TDoピンの信号は次のバウンダリスキャンデバイスのTDiに接続され、順番にPCB上の全てのバウンダリスキャンデバイスを接続し、最後のデバイスからのTDoピンはボードテスタのTDoに接続されます。又ボードテスタからのTCK,TMS信号はバス状に全てのバウンダリスキャンデバイスに接続されます。

バウンダリスキャンデバイスは外部I/Oピンと内部論理との間にバウンダリスキャンセルが配置されTDiピンからの信号とシフトレジスタを構成しており、適当なデータを入力することでバウンダリスキャンセルに接続された任意の出力ピンからデータを出力したり、入力ピンの状態をモニタすることが可能です。PCB上のバウンダリスキャン対応デバイスを一筆書き(デイジーチェイン)に接続することで、ボードテスタからPCB上のバウンダリスキャンデバイスのI/Oピンを制御可能となります。

PCB上のあるネットの試験を行なう場合、そのネットに接続されたデバイスの出力ピンから”L”レベルを出力し、そのネットに接続されたデバイスの入力ピンで”L”を検出し、引き続き出力ピンから”H”レベルを出力し、デバイスの入力ピンで”H”を検出すればそのネットでの2つのデバイスは正常に接続されていると想定できます。

1.3.バウンダリスキャン内蔵レジスタ

バウンダリスキャンデバイスはデバイス本来の内部ロジック機能の他にバウンダリスキャン試験機能を実現するためのレジスタとそのレジスタを制御するためのTAPコントローラが内蔵されています。レジスタへのデータ設定やTAPコントローラの制御のためにTCK,TMS,TDi,TDo,TRST(オプション)の5本の信号が必要となります。

Debug Solutionsへのご連絡:

Copyright © 2001-2006 Debug Solutions